嵌入式零碎知识整理

最近开了门嵌入式的选修课 知识很碎 挑些重点的来cancan

Microsoft Word - 第2章 ARM技术概述.docx (hqyj.com)

ARM9基础知识

ps: 摘自10年前的ppt

ARM9系列微处理器是低功耗的32位RISC结构,最适合要求低成本、低功耗的消费类应用产品。国际许多著名的IT芯片制造公司,基于ARM9处理器核生产了多种微控制器芯片,如三星公司的S3C2410、Atmel公司的AT91RM9200、Intel公司的PXA255、Motorola公司的MC9328、Cirrus Logic公司的EP93XX系列、等等。

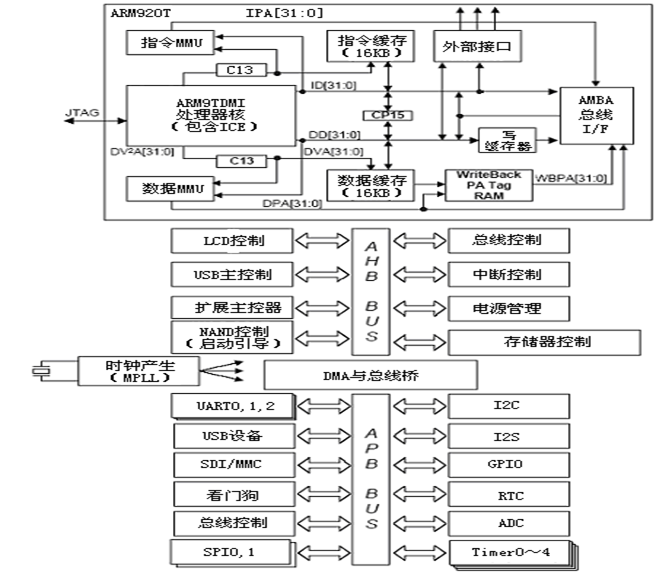

ARM920T CPU结构

(247条消息) arm920t架构cpu详解_静思心远的博客-CSDN博客_arm920t

建议阅读

ARM920T微处理器的指令流水采用了典型的RISC五级流水线结构,将指令执行过程分为取指、译码、执行、访存和写回5个步骤。五级流水线结构采用分离指令cache和数据cache,将每一个指令处理分配到5个时钟周期内,在每一个时钟周期内同时可能有5个指令在执行,消除了指令执行的性能瓶颈,加快了指令执行速度。

ARM9 系列微处理器在高性能和低功耗特性方面提供最佳的性能。具有以下特点:

- 5 级整数流水线,指令执行效率更高

- 提供 1.1MIPS/MHz 的哈佛结构

- 支持 32 位 ARM 指令集和 16 位 Thumb 指令集

- 支持 32 位的高速 AMBA总线接口

- 全性能的 MMU,支持 Windows CE、Linux、Palm OS等多种主流嵌入式操作系统

- MPU支持实时操作系统

- 支持数据 Cache 和指令Cache,具有更高的指令和数据处理能力。

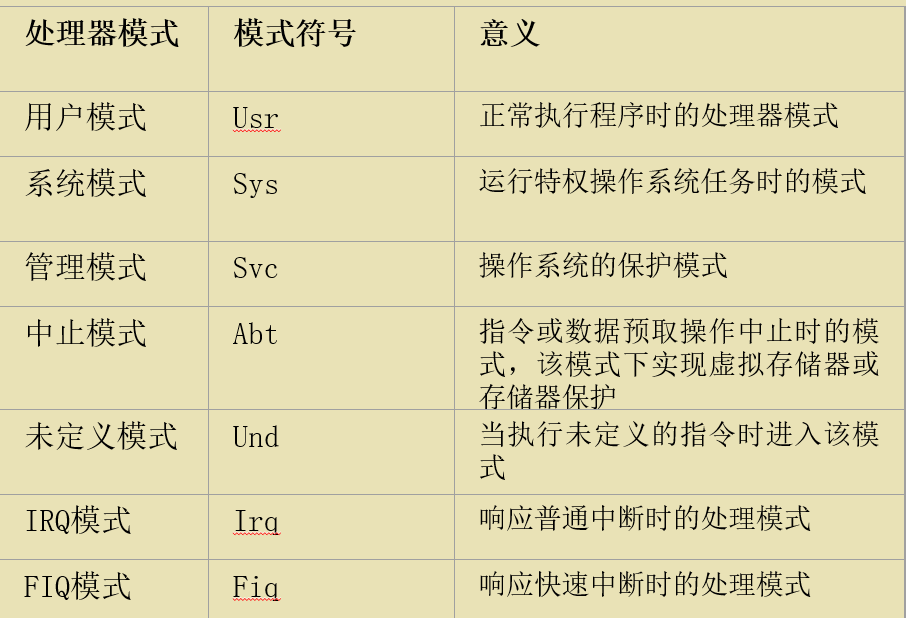

7种模式

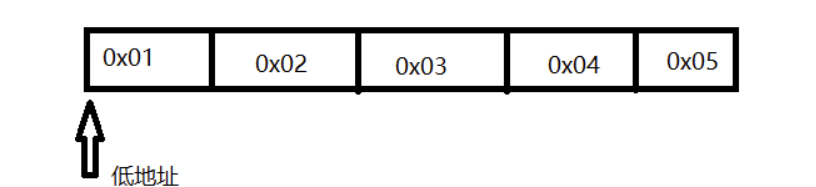

大端模式:就是高位字节排放在内存的低地址端,低位字节排放在内存的高地址端。

(其实,大端模式才是我们直观上认为的模式,但实际并不是这样)

数据 0x0102030405

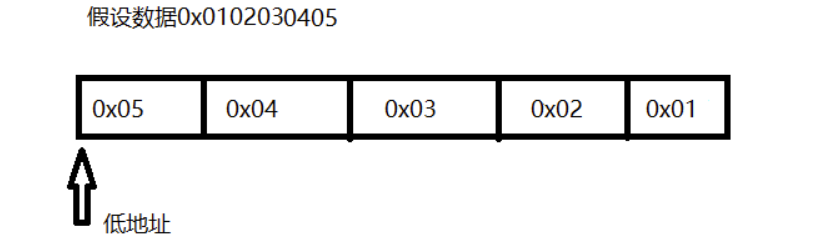

小端模式:就是低字节排放在内存的低地址端,高位字节排放在内存的高地址端。

小端存储模式是ARM9处理器的默认模式。ARM9汇编指令集中,没有相应的指令来选择是采用大端存储系统还是小端存储系统,但可以通过硬件输入引脚来配置它

分支指令

https://blog.csdn.net/mmphhh/article/details/100150806

目的地址=当前执行的指令地址+8+偏移量

https://blog.csdn.net/qq_38365495/article/details/80537000

ARM指令集

https://blog.csdn.net/dddxxxx/article/details/47130545

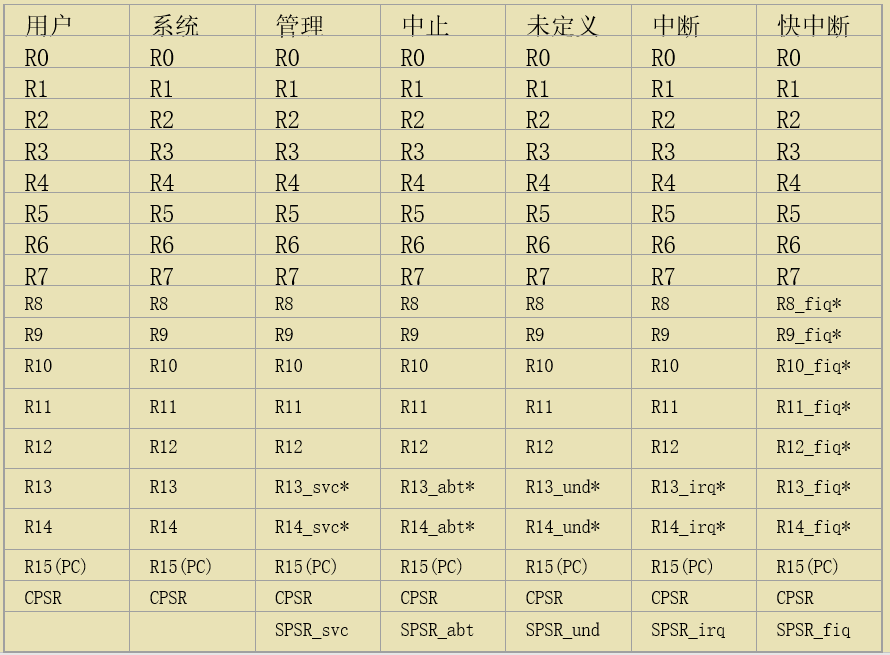

ARM9处理器的内部总共有37个32位的寄存器,其中31个用作通用寄存器,6个用作状态寄存器,每个状态寄存器只使用了其中的12位。这37个寄存器根据处理器的状态及其工作模式的不同而被安排成不同的组。程序代码运行时涉及的工作寄存器组是由ARM9微处理器的工作模式确定的。

- R0 ~ R15称为通用寄存器,其中,R0 ~ R7是不分组的寄存器;R8 ~ R14是根据工作模式进行分组的寄存器;R15是程序计数器,也是不分组的

- R0 ~ R7寄存器是不分组的,在所有的工作模式下,它们物理上是同一个寄存器。

- R8 ~ R14是分组寄存器,它们中的每一个寄存器根据当前工作模式的不同,所访问的寄存器实际可能不是同一个物理寄存器。

- R13寄存器的作用通常是堆栈指针,又称为SP。每种异常模式都有对应于该模式下的R13物理寄存器。

- R14寄存器可用作子程序链接寄存器,又称为LR(Link Register)。当ARM9处理器执行带链接的分枝指令(如:BL指令)时,R14保存R15的值。当异常发生时,相应的寄存器分组R14_svc、R14_abt、R14_und、R14_irq和R14_fiq用来保存R15的返回值

- wR15寄存器的功能是程序计数器,又称为PC。在ARM状态下,R15寄存器的[1:0]位为0b00,[31:2]位是PC的值;

- CPSR寄存器称为当前程序状态寄存器,又称为R16。在所有处理器模式下,CPSR都是同一个物理寄存器,它保存了程序运行的当前状态。在各种异常模式下,均有一个称为SPSR的寄存器用于保存进入异常模式前的程序状态,即当异常出现时,SPSR中保留CPSR的值。CPSR和SPSR均为32位的寄存器,其格式如下

https://blog.csdn.net/david_luyang/article/details/6276533

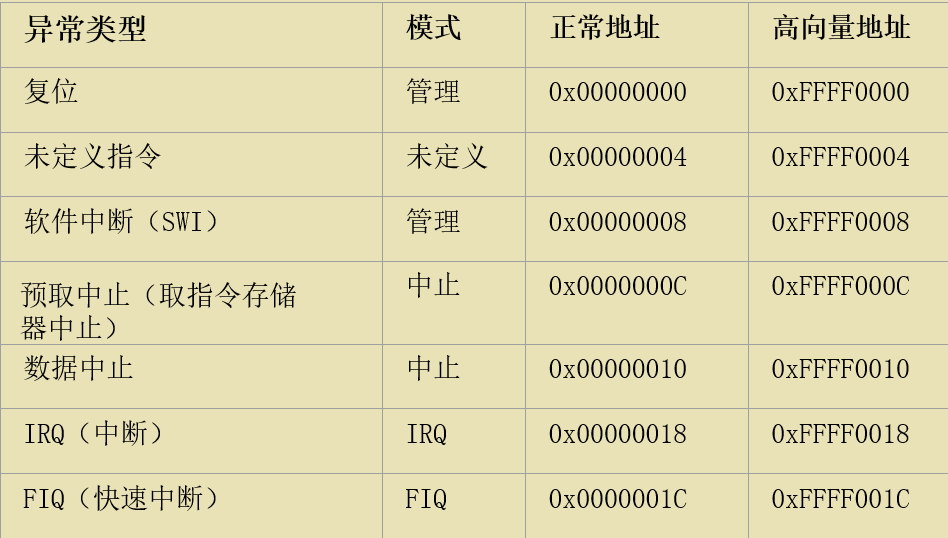

异常

只要正常的程序流程被暂时停止,则异常发生。或者说,异常是由内部或外部产生一个引起处理器处理的事件,例如,外部中断或处理器执行一个未定义的指令都会引起异常。在处理异常之前,处理器状态必须保留,以便在异常处理程序完成后,原来的程序能够重新执行。同一时刻可能会出现多个异常

ARM支持7种类型的异常处理,如下表。异常出现后处理器强制从异常类型所对应的固定存储器地址开始执行程序,这些存储器地址称为异常向量(exception vectors)

BootLoader

讲了一个 “S3C2410芯片的嵌入式系统引导(启动)程序Startup.s文件中的汇编源程序”

不说不知道 一搜才知道 这玩意是三星的

这特么能教我们点更早的东西吗 找的文章都是十年前的了。。。

国内搜的都是一堆乱七八糟的东西 最后在github上找到了源代码

1 | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |

网上找了半天 也没找到什么合适的解读(甄会选教学资料 看来只能自己啃了

老师的课件就是从十年前一个不知名的blog上随便抄下来的 真特么负责任